#电子书截图

#电子书简介

第1章 半导体器件

1.1 N型半导体和P型半导体

1.2 二极管

1.3 金属氧化物半导体场效晶体管

1.4 电容和电感

第2章 集成电路制造工艺发展趋势

2.1 引言

2.2 横向微缩所推动的工艺发展趋势

2.2.1 光刻技术

2.2.2 沟槽填充技术

2.2.3 互连层RC延迟的降低

2.3 纵向微缩所推动的工艺发展趋势

2.3.1 等效栅氧厚度的微缩

2.3.2 源漏工程

2.3.3 自对准硅化物工艺

2.4 弥补几何微缩的等效扩充

2.4.1 高k金属栅

2.4.2 载流子迁移率提高技术

2.5 展望

参考文献

第3章 CMOS逻辑电路及存储器制造流程

3.1 逻辑技术及工艺流程

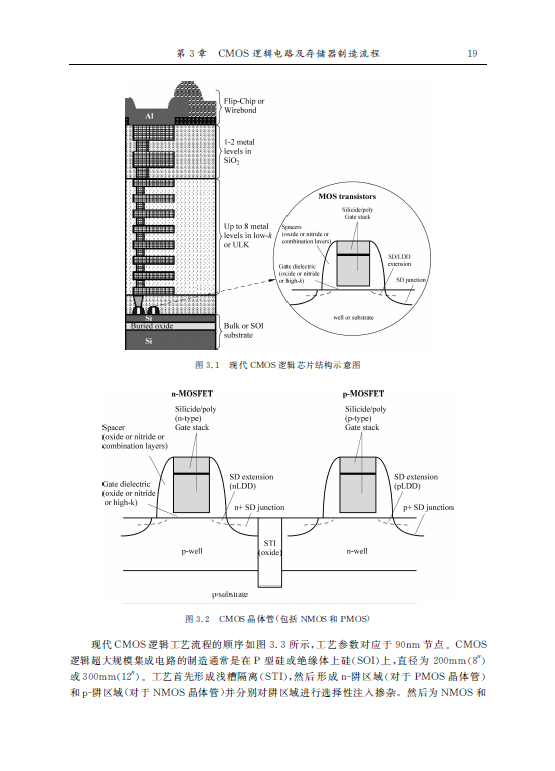

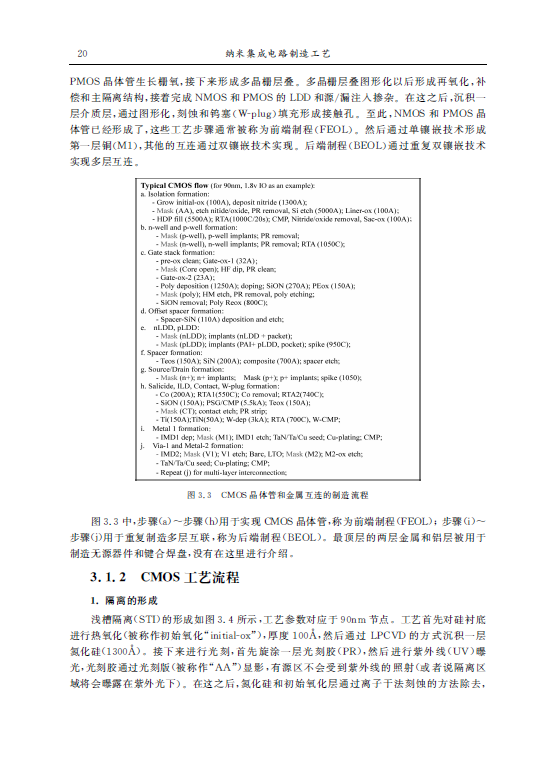

3.1.1 引言

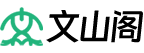

3.1.2 CMOS工艺流程

3.2 存储器技术和制造工艺

3.2.1 概述

3.2.2 DRAM和eDRAM

3.2.3 闪存

3.2.4 FeRAM

3.2.5 PCRAM

3.2.6 RRAM

3.2.7 MRAM

参考文献

第4章 电介质薄膜沉积工艺

4.1 前言

4.2 氧化膜/氮化膜工艺

4.3 栅极电介质薄膜

4.3.1 栅极氧化介电层-氮氧化硅(SiOxNy)

4.3.2 高k栅极介质

4.4 半导体绝缘介质的填充

4.4.1 高密度等离子体化学气相沉积工艺

4.4.2 O3-TEOS的亚常压化学气相沉积工艺

4.5 超低介电常数薄膜

4.5.1 前言

4.5.2 RC delay对器件运算速度的影响

4.5.3 k为2.7-3.0的低介电常数材料

4.5.4 k为2.5的超低介电常数材料

4.5.5 Etching stop layer and copper barrier介电常数材料

参考文献

第5章 应力工程

5.1 简介

5.2 源漏区嵌入技术

5.2.1 嵌入式锗硅工艺

5.2.2 嵌入式碳硅工艺

5.3 应力记忆技术

5.3.1 SMT技术的分类

5.3.2 SMT的工艺流程

5.3.3 SMT氮化硅工艺介绍及其发展

5.4 双极应力刻蚀阻挡层

5.5 应力效应提升技术

参考文献

第6章 金属薄膜沉积工艺及金属化

6.1 金属栅

6.1.1 金属栅极的使用

6.1.2 金属栅材料性能的要求

6.2 自对准硅化物

6.2.1 预清洁处理

6.2.2 镍铂合金沉积

6.2.3 盖帽层TiN沉积

6.3 接触窗薄膜工艺

6.3.1 前言

6.3.2 主要的问题

6.3.3 前处理工艺

6.3.4 PVD Ti

6.3.5 TiN制程

6.3.6 W plug制程

6.4 金属互连

6.4.1 前言

6.4.2 预清洁工艺

6.4.3 阻挡层

6.4.4 种子层

6.4.5 铜化学电镀

6.4.6 洗边和退火

6.5 本章 总结

参考文献

第7章 光刻技术

第8章 干法刻蚀

第9章 集成电路制造中的污染和清洗技术

第10章 超浅结技术

第11章 化学机械平坦化

第12章 器件参数和工艺相关性

第13章 可制造性设计

第14章 半导体器件失效分析

第15章 集成电路可靠性介绍

第16章 集成电路测量

第17章 良率改善

第18章 测试工程

第19章 芯片封装

《纳米集成电路制造工艺》共分19章,涵盖先进集成电路工艺的发展史,集成电路制造流程、介电薄膜、金属化、光刻、刻蚀、表面清洁与湿法刻蚀、掺杂、化学机械平坦化,器件参数与工艺相关性,DFM(Design for Manufacturing),集成电路检测与分析、集成电路的可靠性,生产控制,良率提升,芯片测试与芯片封装等项目和课题。

国内从事半导体产业的科研工作者、技术工作者和研究生可使用《纳米集成电路制造工艺》作为教科书或参考资料。

超大规模集成电路的生产工艺,从“微米级”到“纳米级”发生了许多根本上的变化。甚至,从45nm缩小至28nm(以及更小的线宽)也必须使用许多新的生产观念和技术。

张汝京先生是随着半导体产业的发展成长起来的领军人物,见证了几个技术世代的兴起与淘汰。他本人有着深厚的学术根基,以及丰富的产业经验,其带领的团队是多年来在业界top半导体代工厂一线工作的科研人员,掌握了业界领先的制造工艺。他们处理实际问题的经验以及从产业出发的独特技术视角,相信会给读者带来启发和帮助。

20世纪40年代贝尔实验室的科学先进们发明了晶体管,20世纪50年代德州仪器公司和仙童公司的科技大师们分别发明并推展了集成电器的生产技术,20世纪60-70年代大规模生产半导体器件的技术在美国、欧洲及亚洲也蓬勃发展开来。20世纪80年代-迄今,超大型集成电路的设计和生产工艺继续不断以惊人的速度,几乎按着“摩尔定律”不断地加大半导体器件的集成度,而超大型芯片在“线宽”(CD)上也以倍数的形式进行着细微化。自2000年起集成电路的线宽也从“微米级”进入了“纳米级”。2010年起我国先进的半导体生产工艺也从45纳米延伸至28纳米以及更小的线宽。超大规模集成电路的生产工艺,从“微米级”到“纳米级”发生了许多根本上的变化。甚至,从45纳米缩小至28纳米(以及更小的线宽)也必须使用许多新的生产观念和技术。

清华大学的王志华教授于2010年就提议由国内熟悉这类工艺的学者、专家、工程师们共同编撰一本较为先进的半导体工艺教科书,同时也可以供半导体厂的工作人员作为参考资料之用,内容要能包含45纳米、32纳米至28纳米(或更细微化)的工艺技术。本人非常荣幸有机会来邀请国内该领域的部分学者、专家、工程师们共同编写这本书。本书的初稿是用英文写作的,国内学校的许多老师和半导体业界的先进、朋友们希望我们能用中文发行这本书,好让更多的研究所学生、工程师、科研同行更容易阅读并使用本书。我们接着邀请清华大学的教授、老师们将全书翻译成中文,同时也与各方联系取得引用外部资料的许可,清华大学出版社的编辑也帮我们进行编辑加工。几经审稿、改订等大量的工作,本书历时四年多终于完成了!

本书共分19章,涵盖先进集成电路工艺的发展史,集成电路制造流程、介电薄膜、金属化、光刻、刻蚀、表面清洁与湿法刻蚀、掺杂、化学机械平坦化,器件参数与工艺相关性,DFM(Design for Manufacturing), 集成电路检测与分析、集成电路的可靠性,生产控制,良率提升,芯片测试与芯片封装等项目和课题。我们在此要特别感谢每一章的作者(和作者群),他们将所知道的最新技术和他们实际工作的经验,尽力地在书中向我们科技界的朋友们一一阐述,也感谢他们为祖国的集成电路科技和协助提升同行朋友们的工艺水平做出的贡献!

我们在此特别题名感谢各位作者(按本书章节次序列名如下); 卢炯平、季明华、向阳辉、何有丰、荆学珍、周鸣、杨瑞鹏、聂佳相、何伟业、伍强、时雪龙、顾一鸣、刘庆炜、张海洋、刘焕新、许开东、陈枫、刘东升、蒋莉、陈昱升、张立夫、郭志蓉、吴启熙、郭强、高强、陈寰、范良孚、林山本、严大生、牛崇实等!若不是以上各位学者、专家和朋友们的撰写、审稿和改正,全心全力的投入带来宝贵的成果,这本书将无法完成!也感谢中芯国际集成电路有限公司提供的许多非常宝贵的协助!

我们也要再次感谢清华大学的各位老师(王志华教授、李铁夫、杨铁博士)和清华大学出版社自始至终的鼓励、支持和鼎力相助,这本书才能完成并展现在广大读者的面前!希望这本书能够以实际资料来启发国内半导体产业的学者、专家、技术工作者和研究生们独有的创新和发明,让我们的半导体产业与日俱进,从制造到创造,再创华夏辉煌盛世!

张汝京敬上2014年3月于上海

评论列表(0)